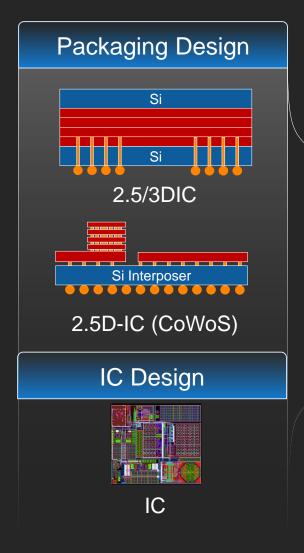

#### Silicon and System First-Pass Success

Advanced-node mixed-signal IC to complex 5G solutions

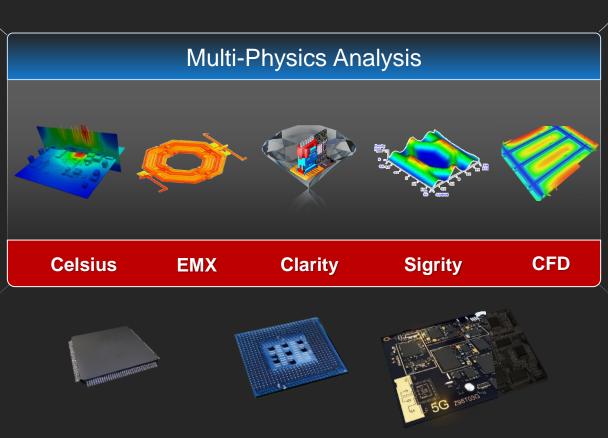

### From the Chip Through to the System Multi-Physics Analysis Portfolio

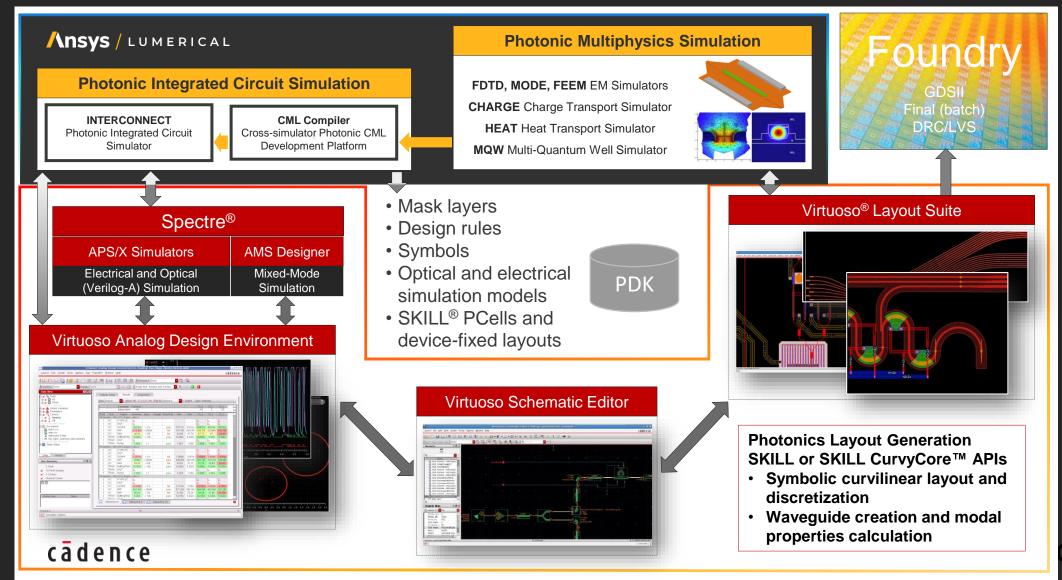

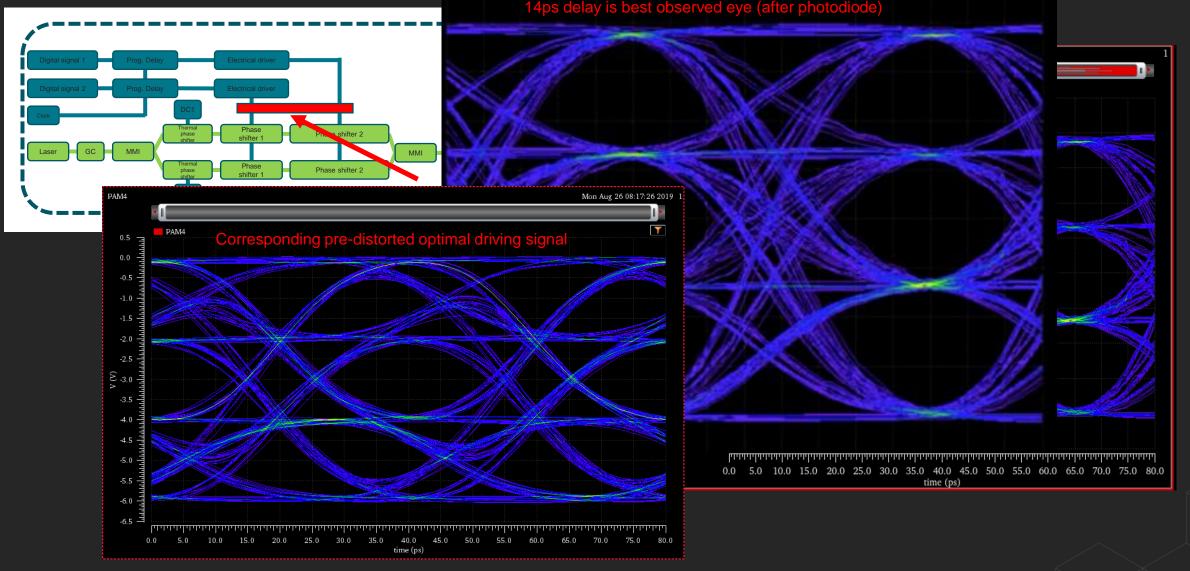

#### Electronic-Photonic Design Automation (EPDA) IC Flow

#### Working with Foundry Partners for Wide, Accessible Enablement

- Foundries are our key partners in the past years

- They presented their PDK as well as their differentiated offering at the annual Cadence Photonics event

## Collaboration to Enable Truly Unique Design Environment (Combining the best in kind...)

#### Collaboration to Enable Truly Unique Design Environment

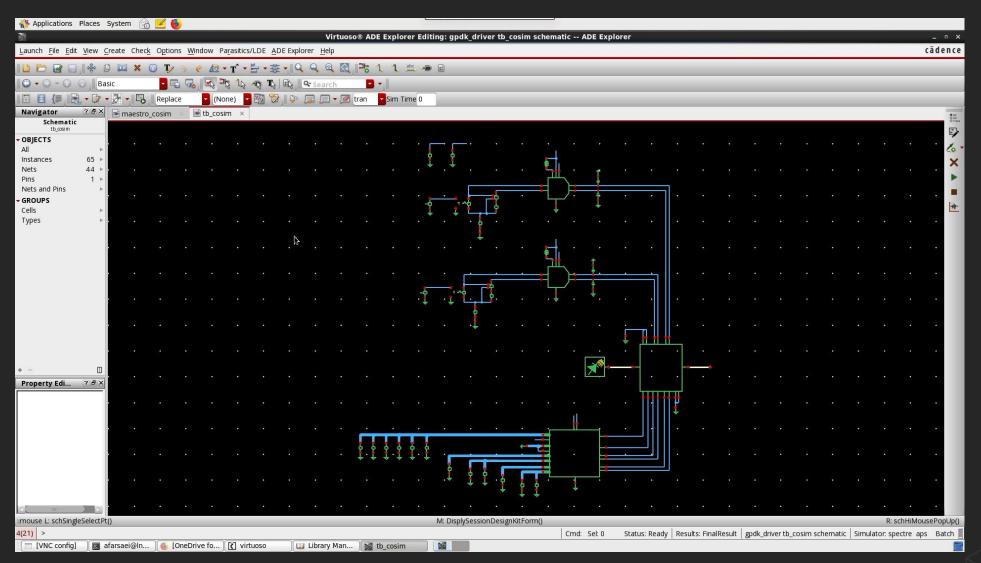

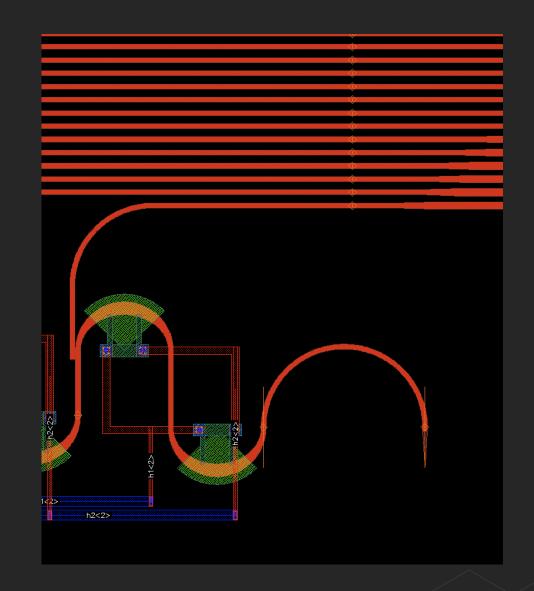

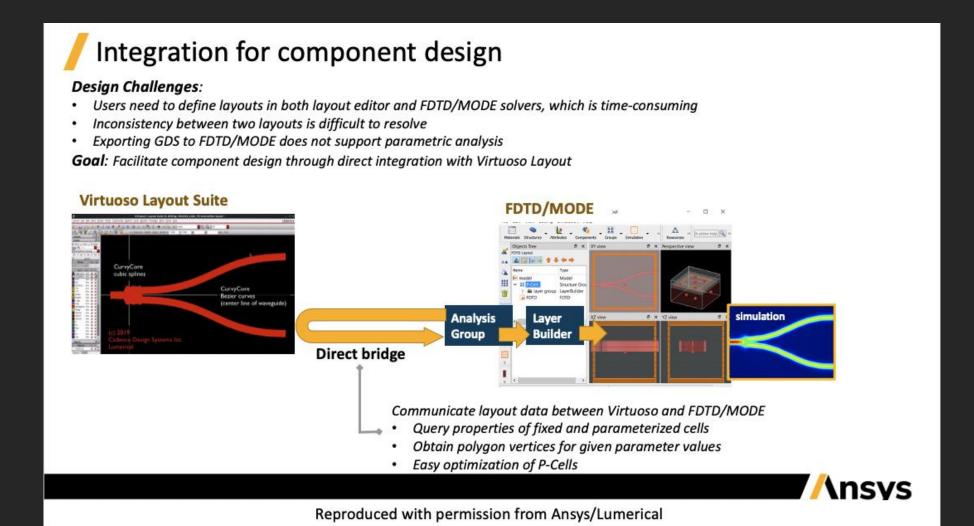

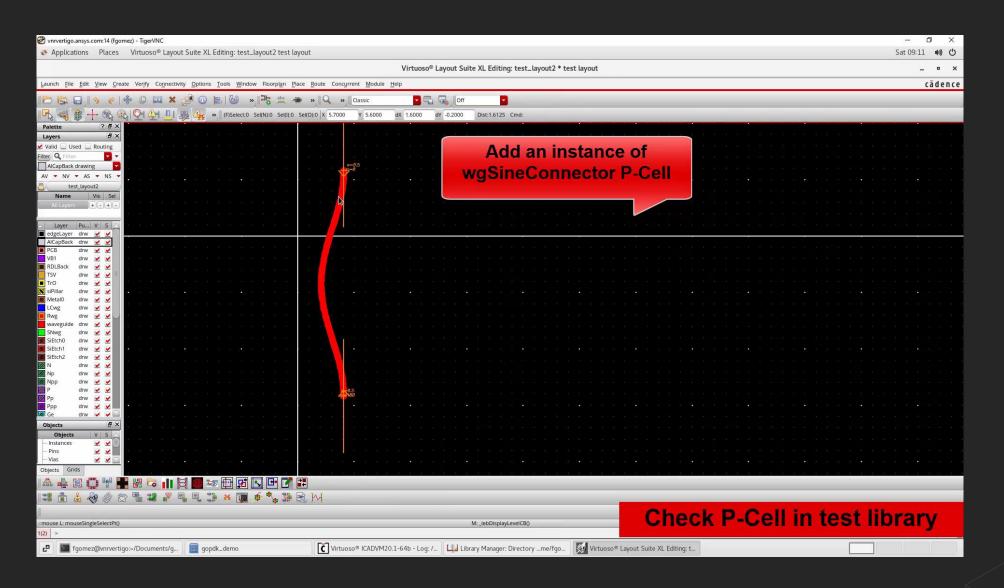

#### Integrated Where It Matters!

- Cadence CurvyCore<sup>™</sup> technology is the native curvilinear engine for the Virtuoso<sup>®</sup> Design Platform (in production since 2018)

- Tower, GF, AIM, CTek... PDKs

- IDMs

- Supports both Interactive or API driven design flows (or a mix)

- Built above base Virtuoso platform inherits years of flow maturity when using this known and proven environment

#### Continuing to Invest

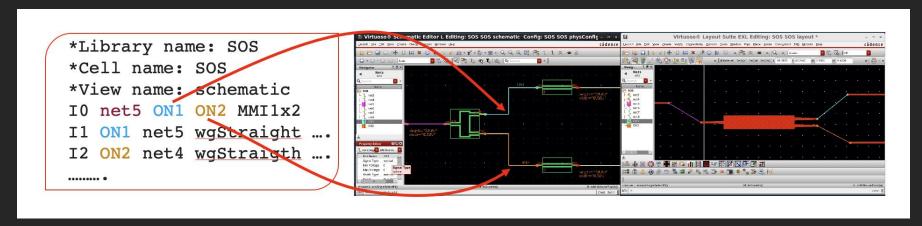

- Support for optical signal in Spectre® simulation (production end of 2019)

- Enables matching connectivity for all representations, even though optical signals can be represented by very complex, multi-quantities (TE Img, Real, forward, backward, TM, and so on) in the model

- Key enabler for EPDA / schematic-driven flows

- Works with Verilog-A or Spectre models

Compatible with Lumerical CML Compiler models

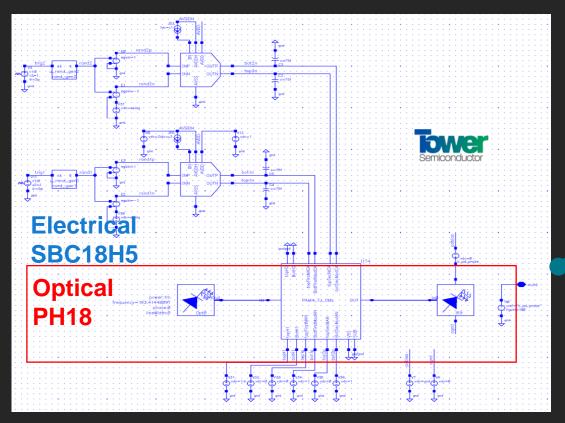

#### Working with Foundries to Validate Models and Model Strategies

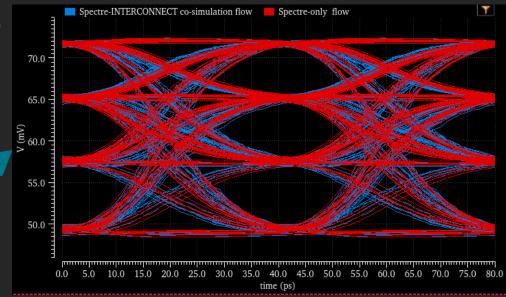

Results presented at CadenceLIVE™ Americas 2021 (ANSYS/Lumerical and Tower Semiconductor)

|                                          | Spectre®-<br>INTERCONNECT flow | Spectre-only       |

|------------------------------------------|--------------------------------|--------------------|

| Electrical element models                | SPICE                          | SPICE              |

| Optical element models                   | INTERCONNECT                   | Photonic Verilog-A |

| Simulation Time                          | 612.4s                         | 237.5s             |

| Extinction Ratio                         | 1.55dB                         | 1.558dB            |

| 10%-90% Rise Time<br>for level0 – level3 | 21.98ps                        | 21.76ps            |

#### Continuing to Partner

#### Continuing to Partner

#### Parting Words

- Need to include thanks to the Lumerical team, which has graciously contributed to this presentation to show a more complete picture

- Cadence is very engaged both at the system analysis level and the PIC level,

driven by the requests from our customers

- José always asks how we can help each other

- I am interested in working with a SiN foundry to enable a commercial SiN PDK

- We work with a lot of startups (not just the big electronic firms) talk to us

# cadence®

© 2022 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="www.cadence.com/go/trademarks">www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or PCI-SIG. All other trademarks are the property of their respective owners.