Electro-Optics MCM

Packaging

for Quantum Computing

Kishor Desai PsiQuantum

January 24, 2022

### Agenda

- Company Profile

- Quantum Computing Architecture Packaging Requirements

- Conventional packaging The Building Block

- Datacenter optics Leading Infrastructure Development

- Recent packaging Trends High Performance Computing (HPC)

- Summary

### About Psi Quantum

PsiQuantum Closes \$450 Million Funding Round to Build the World's First Commercially Viable Quantum Computer

Jul 27 2021 - PsiQuantum Press Release

#### **About PsiQuantum**

Powered by breakthroughs in silicon photonics and quantum architecture, PsiQuantum is on course to build the world's first commercially useful quantum computer to solve some of the world's most important challenges. PsiQuantum believes silicon photonics is the only way to achieve the necessary scale required for error correction and deliver a fault-tolerant, general-purpose quantum computer. With quantum chips now being manufactured in a world-leading semiconductor fab, PsiQuantum is uniquely positioned to deliver quantum capabilities that will drive advances in climate, healthcare, finance, energy, agriculture, transportation, communications, and beyond. To learn more, visit <u>www.psiquantum.com</u>

40 years of IC Packaging Interconnect Development

- From Mainframe computing to now Quantum Computing

- From pluggable connector to now face to face connect

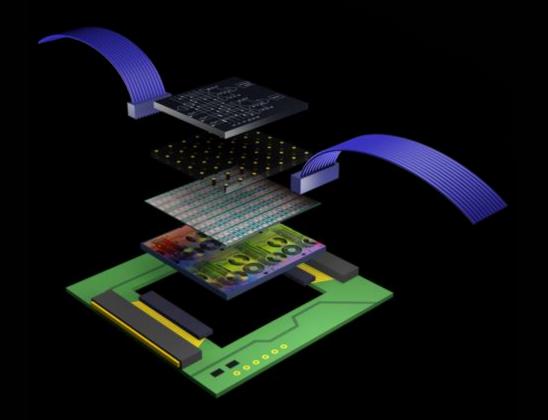

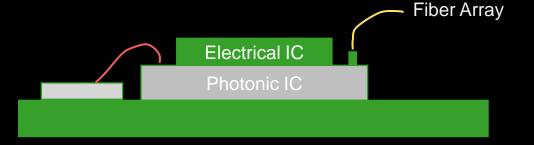

### Quantum Computing Packaging

- 3D Integration of EIC and PIC IC

- Fiber coupling of Optical IO

- Reliability Performance at Cryogenic Temperature

- Validation of Packaging Assembly Processes & Materials

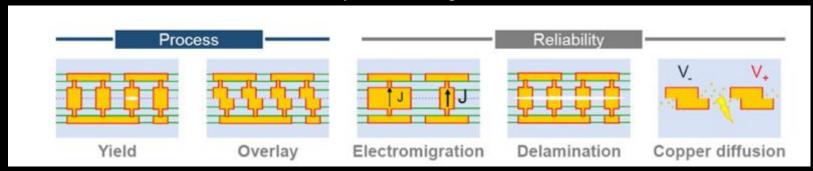

### Flip chip Interconnect – A Building Block for the Advanced Packaging

- Interconnect

- Wire bonding

- Flip chip

- Substrate/Interposer

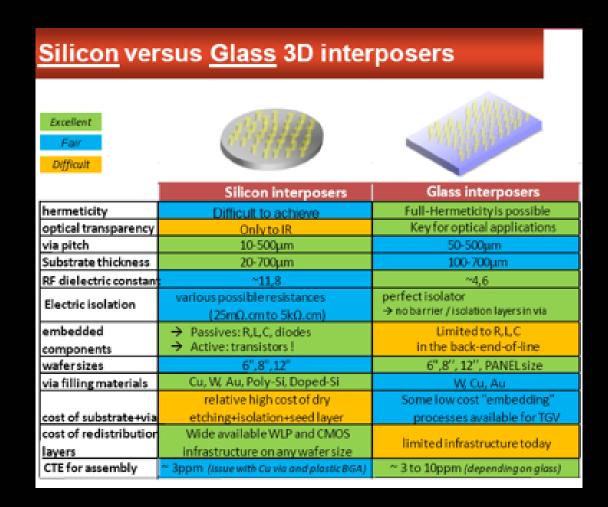

- Ceramic, Laminate, Silicon/Glass

- **Integration Processes**

- Bumping

- Reflow/Thermo Compression Bonding

- Face to Face Bonding

- 2.5D Interposer

- Wafer level Fan Out

Package Substrate IO Density & Performance

Source: ASE, TechSearch

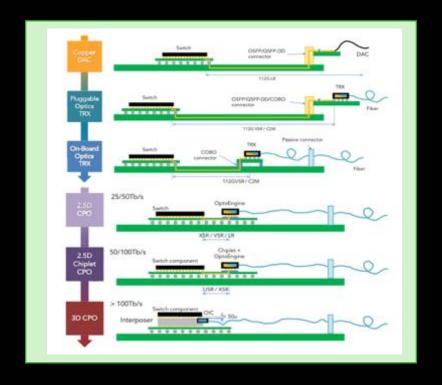

### Datacenter Optics – Evolution to Co-Packaged Optics

- On-board to achieve proximity to the main switch ASIC

- Co-packaged optics is the most attractive solution

- Can realize cost and power reductions of up to 50%.

Source: IET

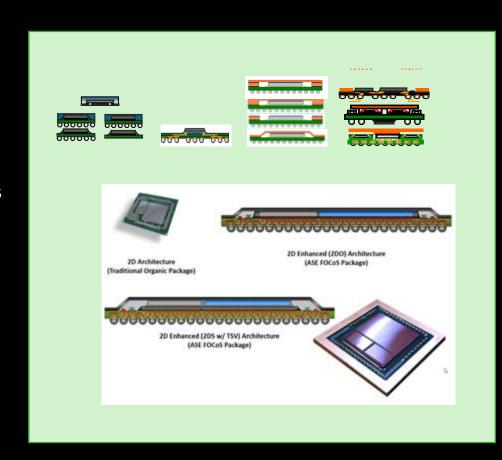

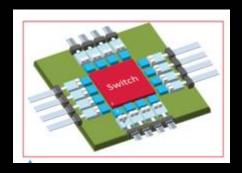

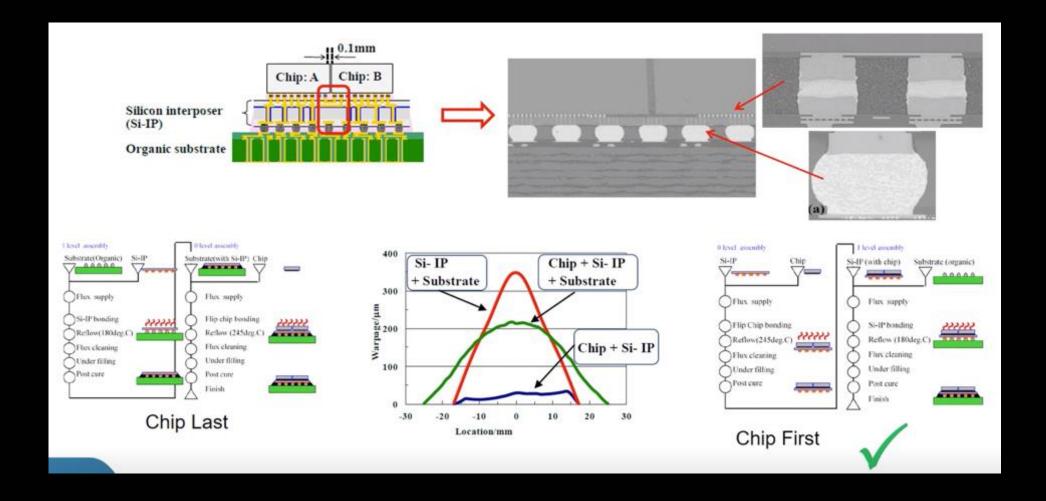

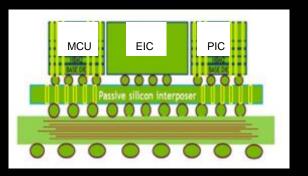

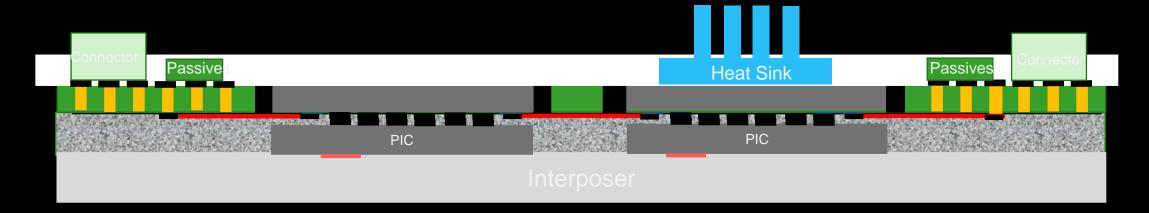

### Electro-Photonic Multi-Chip Module- 2.5D Interposer

Source: A Star/IEEE 2021

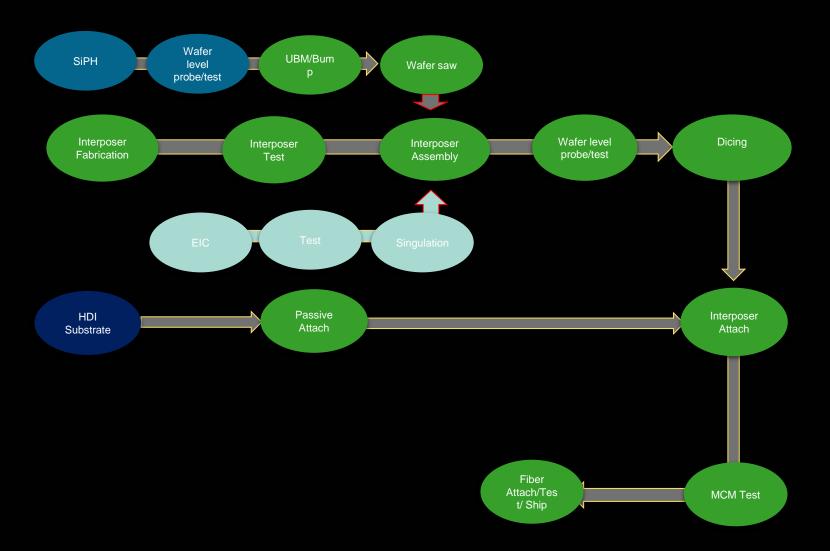

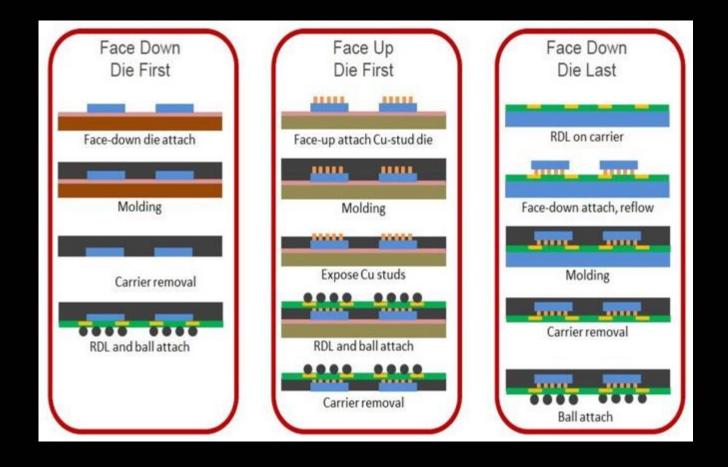

# 2.5D Assembly process flow

Source: Yole Samsung Galaxy

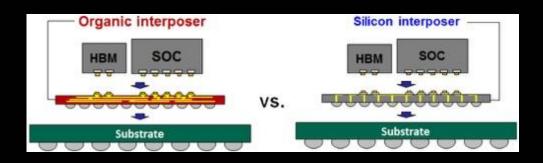

### Electro-Photonic Multi-Chip Module –Interposer

Source: TSMC

High density Silicon Interposer widely used- eg. GPU/HBM Packaging

### Electro-Photonic Multi-Chip Module – Wafer Level Fan-Out

Wafer level fan-out integration is another approach providing high density interconnect for heterogeneous integration of Electronics and Photonics IC Source: Innocentrix

### Electro-Photonic Multi-Chip Module – Wafer Level Fan-Out

- KGI for C2C interconnect using Fan Out Wafer level RDL process

- Silicon interposer with TSV/RDL connections for Passives, Connectors

- Face to Face bonding

- Molding/Underfilling coupling EIC & PIC assembly

- Manufacturing processes Leveraging Industry Infrastructure; Scalable

## Electro-Photonic Multi-Chip Module – 3D

F2F bonding - Solder

**Hybrid Bonding**

- EIC & PIC Face to Face bonding

- Process selection Higher Performance, Higher Yield and Lower cost

- Well established process for CIS and ISP

Source: 3DInCites

ST Micro

### Summary

- Integration of PICs and EICs while meeting key metrics in terms of performance, power density, cost, and thermals requires advanced packaging solutions

- Advanced packaging process that scales with the increase in interconnect density

- Extensive TM modeling is required to down select packaging processes and materials

- Thermal challenges will require solution with the requirements of cooling both the sides of the Package structure

- Packaging interconnect and Material performance in Cryogenic environment needs to be demonstrated working across the suppliers/partners

### Solution Through Collaborative Partnerships with the Industry Infrastructure