#### EPIC World Photonics Technology Summit, January 24<sup>th</sup>, 2022

# High Volume Silicon Photonics for Optical I/O and other Next Generation Applications

Robert Blum – robert.blum@intel.com

**Intel Corporation**

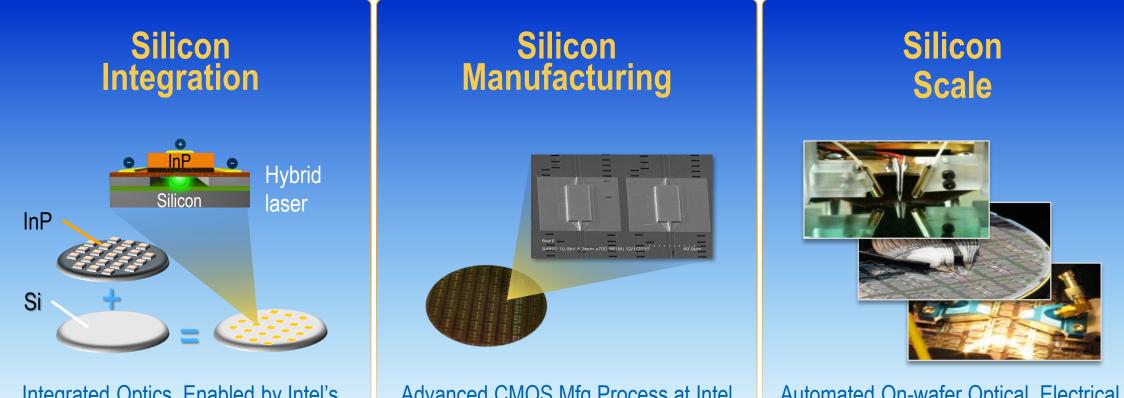

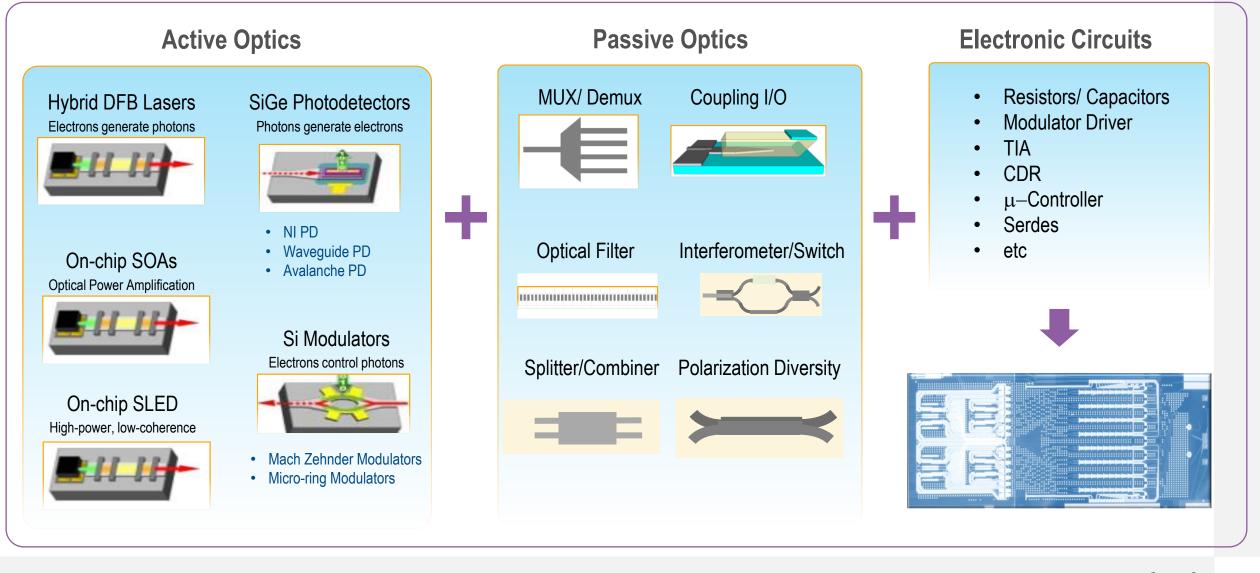

### Intel Silicon Photonics: Optics at Silicon Scale

Integrated Optics, Enabled by Intel's Hybrid Laser Technology InP for lasers, SOAs, PDs Advanced CMOS Mfg Process at Intel Fabs On 300mm Wafers

Automated On-wafer Optical, Electrical, and High-speed Test Wafer-level burn-in

#### Wafer-scale manufacturing of optical sub-assembly; known good die at wafer level

2

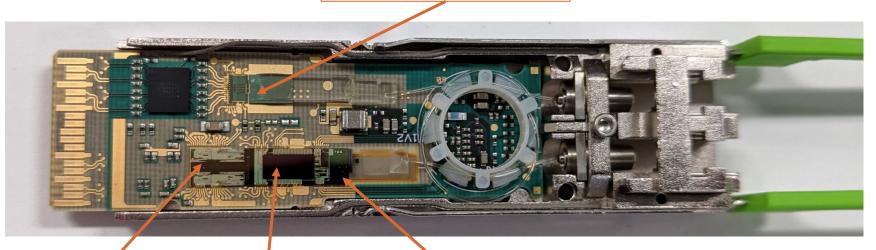

### Silicon Photonics High Volume Transceivers 100G CWDM4 with No Hermetic Packaging, 5M+ units shipped

4 photodiodes (Rx)

4 lasers 4 modulators Optical mux +MPDs +monitor/control

- Transmitter chip integrates 4 lasers, 4 modulators, optical multiplexer, and related monitor/control functions on a single die

- Receive path is a separate chip with 4 high speed photodiodes

- Data center operation or industrial temperature range (-40°C to 85°C)

- Industry-leading reliability and quality: ~2 FIT for laser; ~30dppm for module

#### 200G and 400G optics also in production and shipping in volume now; 800G sampling

3

intel

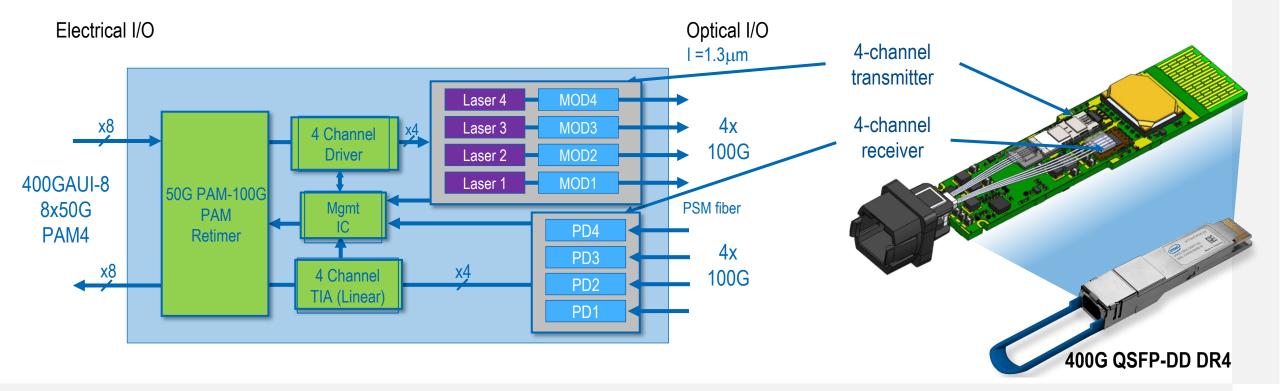

### 400G DR4 Silicon Photonics Optical Transceiver

- 400G Ethernet connectivity for 12.8T Ethernet switches

- Standards-compliant optical interface with extended 2km reach for 400G or 4x100G breakout

- In volume production to support hyperscale data centers

4

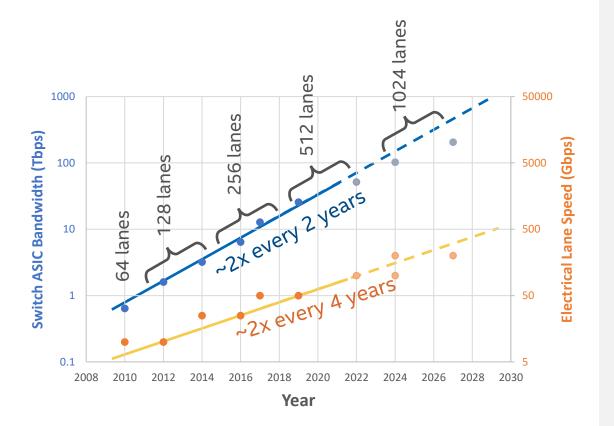

Datacenter Network Bandwidth Scaling Fundamental challenge: I/O vs. switch scaling

- Switch: 2x bandwidth every ~2 years

- Power efficiency with process node

- I/O: 2x data rate every 3-4 years

- Diminishing returns in power efficiency

- Increasing share of switch ASIC power consumed by I/O

- Increasing share of link power consumed by first and last 12"

- 40% at 100G lanes

- Increasing packaging and signal integrity complexity (\$)

Directional, based on Intel estimates

intel

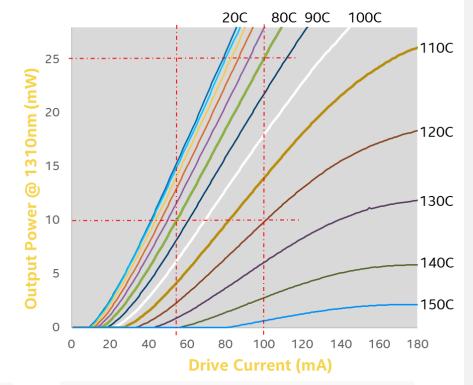

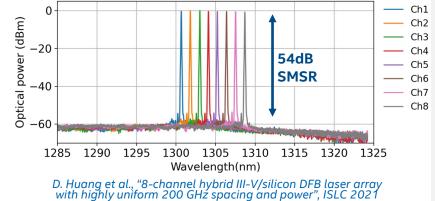

### DFB Laser Performance

Excellent performance over temperature

- Laser emission up to 150C

- 10mW at 80C for 60mA; 25mW at 80C for 100mA

Uncooled operation enabled by tight process control on 300mm wafer

- Low relative intensity noise (RIN) < -155 dB / Hz

- High side-mode suppression ratio (SMSR) > 40dB

Source: P. Doussiere, "Laser integration on silicon," GROUP IV PHOTONICS, 2017 H. Yu, "400Gbps Fully Integrated DR4 Silicon Photonics Transmitter for Data Center Applications," OFC, 2020

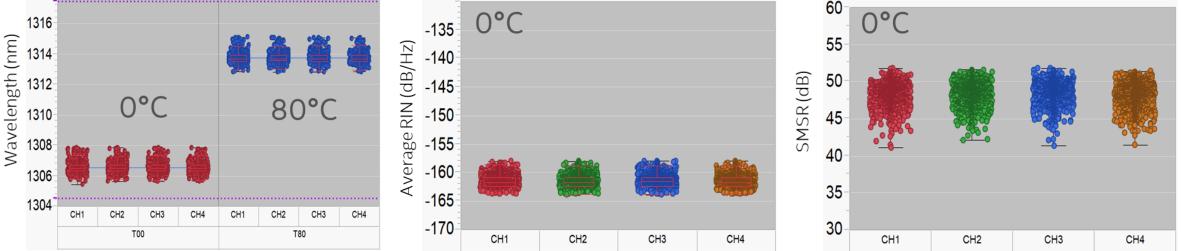

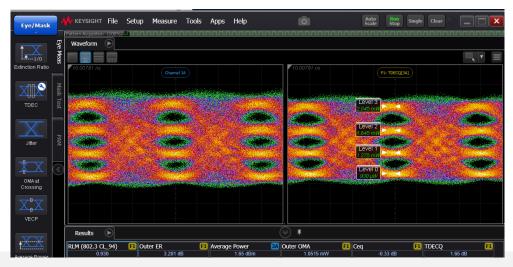

### High-speed 6-mm Micro-Ring Modulator

✓ 8x128Gb/s = 1024Gb/s

Meer Sakib et al., "260 Gb/s/λ PDM Link with Silicon Photonic Dual-Polarization Transmitter and Polarization Demultiplexer", Tu4D.1, ECOC 2021

7

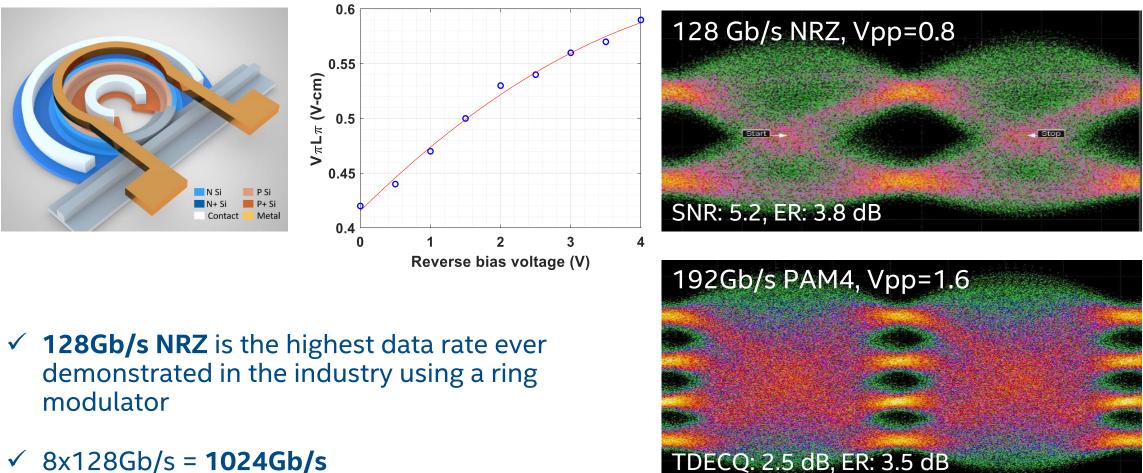

## Silicon Photonic Integrated Circuit

Integrate all Photonic Components On-Chip to Scale BW-Density & Cost

- Germanium diodes

- 106 Gbps PAM4 capable

>30cm of WG routing>600 active bumped pads4x Temperature sensors

intel

8

EPIC WPTS, San Francisco, January 24<sup>th</sup>, 2022

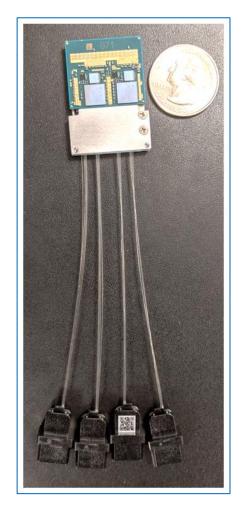

S. Fathololoumi, "1.6Tbps Silicon Photonics Integrated Circuit for Co-Packaged Optical-IO Switch Applications", OFC 2020

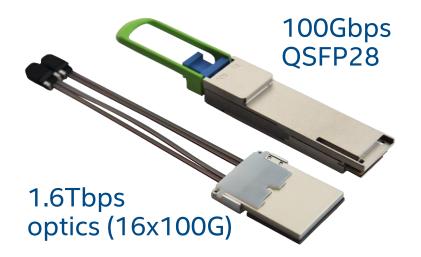

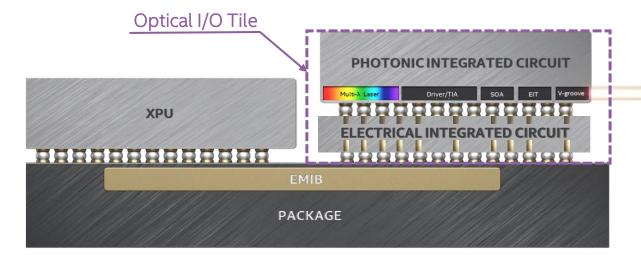

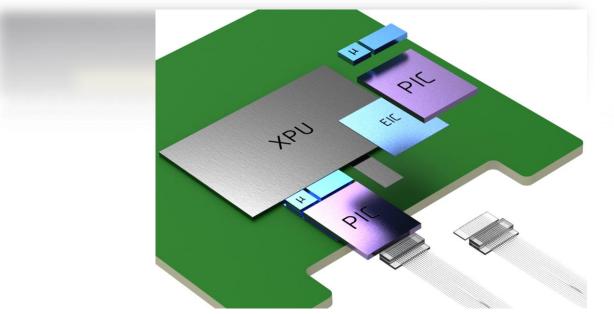

### Co-packaged optics tile

40x bandwidth density >30% energy efficiency improvement

Another >2x density and 15% efficiency improvement projected with 3.2T CPO module product

- Active development towards product intercept with 3.2T tile for 51.2T parallel and WDM optics in standards-compliant CPO module

- Hybrid integration 2.5D package of PIC and EIC

- Optimized and on different cadence

- High-speed, high-density LGA socket on bottom compatible with XSR channel

- Yield and testability ("Known Good Tile")

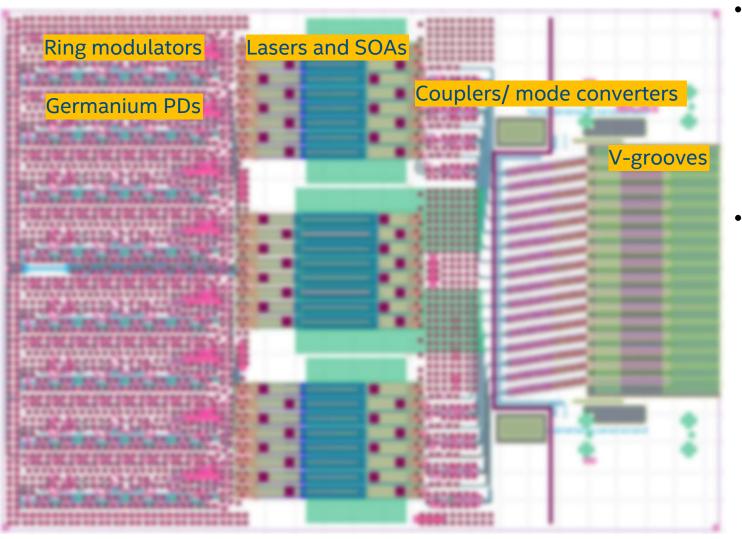

- Passive alignment enabled by mode converters and V-grooves

Ling Liao, "Silicon Photonics Co-Packaged Switch", Hot Interconnect 2020 Ken Brown, "Packaging Technology for coming generations of Silicon Photonics", Semicon Taiwan 2020

intel

9

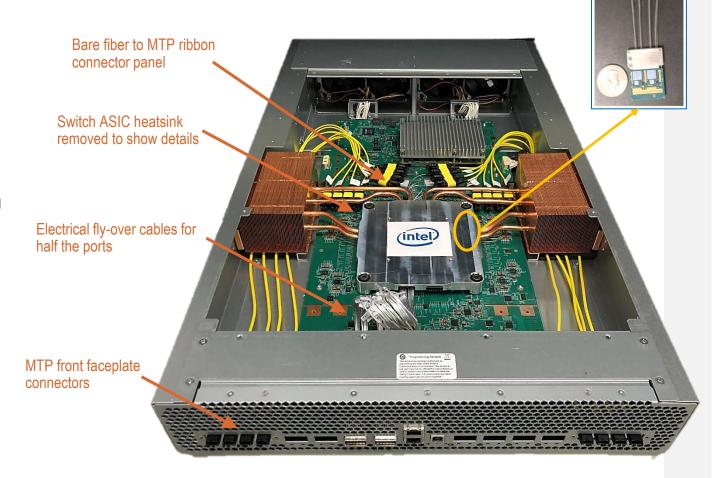

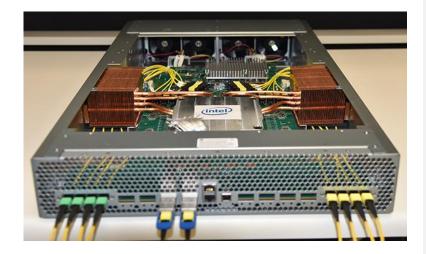

### March 2020 Demonstration of Industry-First Co-Packaged Optics Ethernet Switch

- Barefoot Tofino 2 12.8T P4-programmable Ethernet switch

- Co-packaged with integrated photonic engines

- 16x lasers coupled to 16x 106 Gbps PAM4 ring modulators = 1.6Tbps aggregate bandwidth

- Live 400G Ethernet traffic enabled by fully functional switch platform with co-packaged optics ports in single switch package

### Co-packaged optics

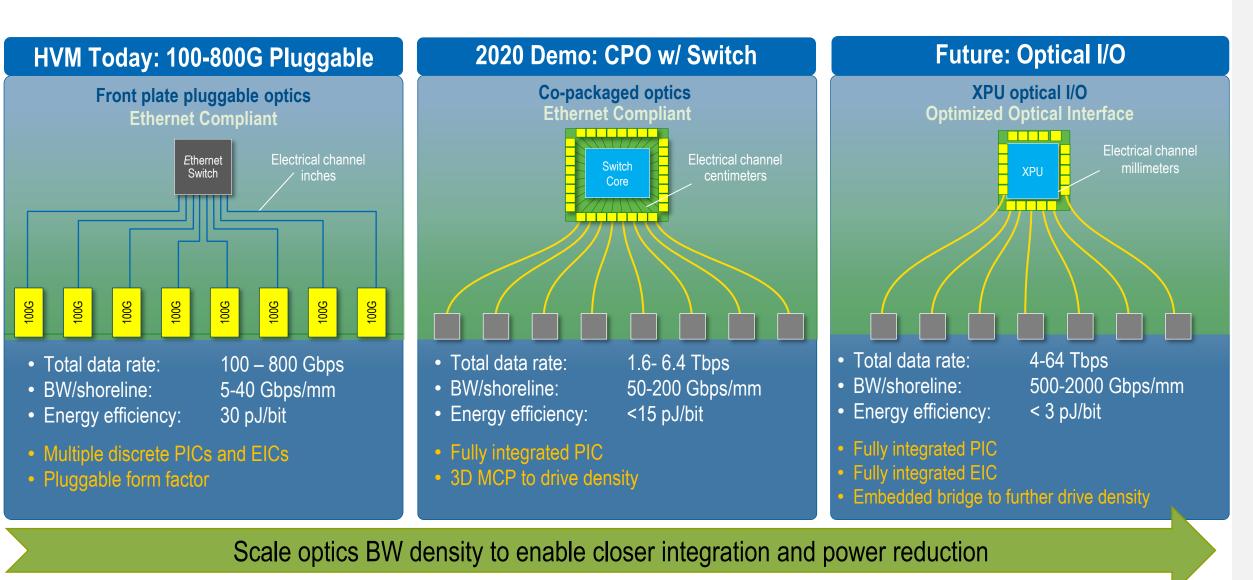

- Growth in bandwidth requirements is not slowing down but power trajectory is unsustainable

- Closer integration of optics to ASIC reduces system I/O power, while supporting continued scaling

- Scaling to 51Tbps switches under development;

- Air-cooling @ >1kW challenging, but feasible

- Power rail noise will likely be the biggest PDN challenge

- Multi-vendor eco-system possible, but timeline is tight

- Broad adoption at 100T as enabling technology for scalability

- With 200G I/O and 200G/ $\!\lambda$

- Development of healthy eco-system around open standards is critical to support commercialization

- Agreement on test points and performance targets

- Beyond switches: Co-packaged optics will be the enabling technology for bandwidth scaling across a broad range of SoCs

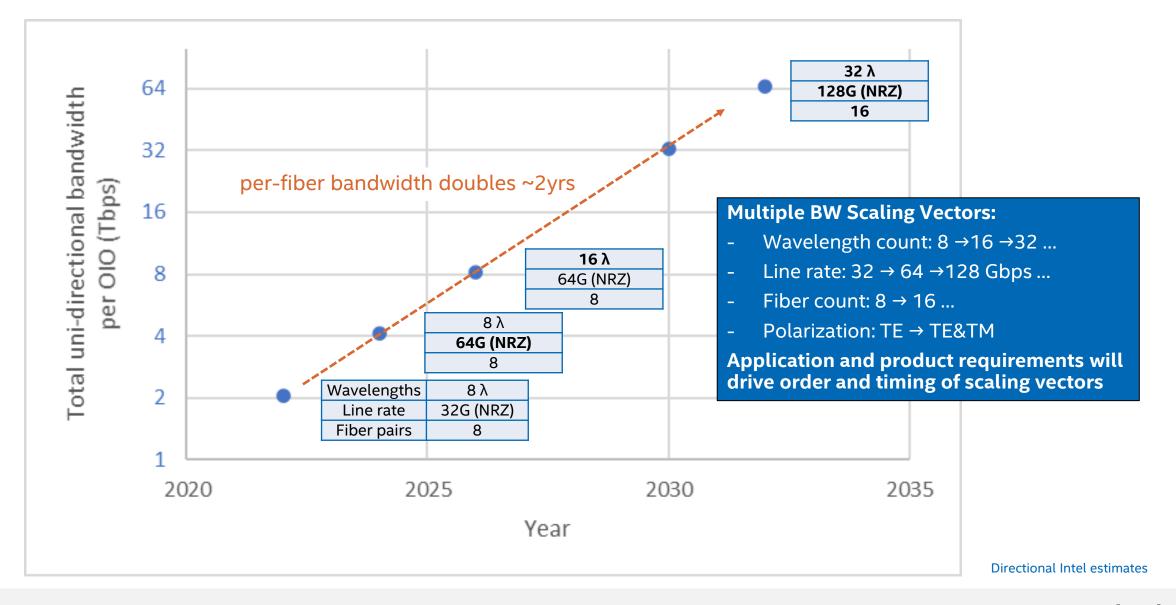

### Silicon Photonics Enables Path to Performance Scaling

Intel estimates, values for directional purposes

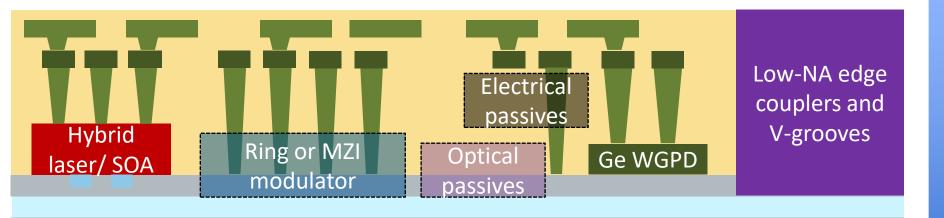

## 8 Tb/s Photonic IC for Optical I/O

- 8 Tb/s total bi-directional bandwidth

- $8\lambda \times 64$  Gbps NRZ per fiber

- 8 fibers for transmit; 8 for receive

- On-die lasers and amplifiers

- High speed ring modulators

- High speed Ge photodetectors

- Polarization diverse design

- Low-NA couplers & V-grooves for fiber coupling

- High volume platform for optical I/O

- Compact size through ring resonators and 8channel multiplexing

- 8ch on-chip DFB array with 200GHz channel spacing

## What to Expect from Optical I/O by 2023

#### Ultra-high bandwidth

~1Tbps per fiber

#### Reach

>100m, orders of magnitude better than electrical I/O

#### **Shoreline Density**

>4x improvement over PCIe6

### **Energy Efficiency**

Trending to 3pJ/b (65% of PCIe6)

#### Latency

<10ns + TOF, comparable to electrical I/O

### OIO Bandwidth Scaling Trajectory

### Most Integrated Silicon Photonics Process

#### Additional process features:

- High efficiency phase modulation

- Wafer-level trimming technology

- Avalanche waveguide photodetectors (optional)

- Electrical passives (resistor and capacitor)

- Optical passives (MMI, Polarization splitting & rotation, MUX/DEMUX, etc.)

- V-grooves for fiber alignment (optional)

- Compatible with flipchip Tx/Rx IC assembly

## Components in Silicon Photonic Integrated Circuits

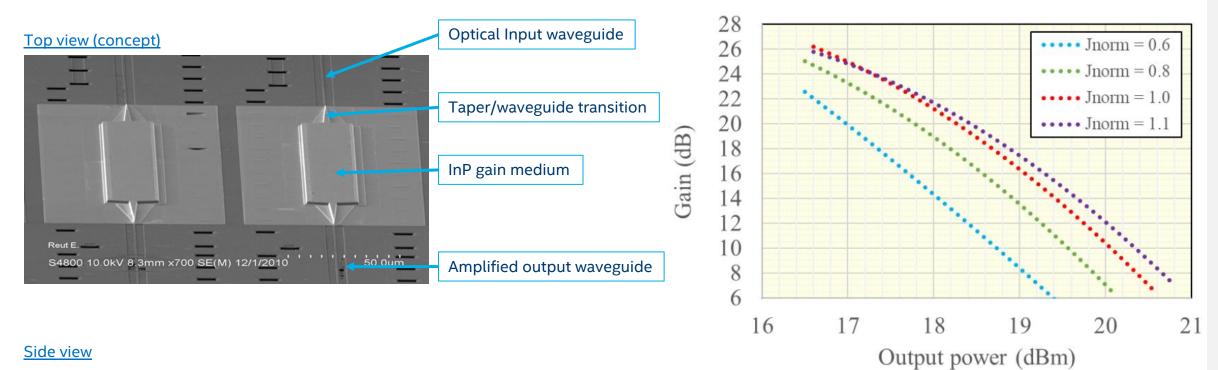

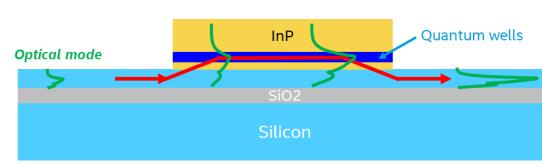

### Optical On-Chip Amplifiers Enable High Output Power

100mW (20dBm) output power from semiconductor optical amplifiers (SOAs)

On-chip SOAs are unique differentiation for Intel hybrid integration platform

J. K. Doylend, S. Gupta, "An overview of silicon photonics for LIDAR," Proc. SPIE 11285, Silicon Photonics XV, (SPIE OPTO/Photonics West 2020)

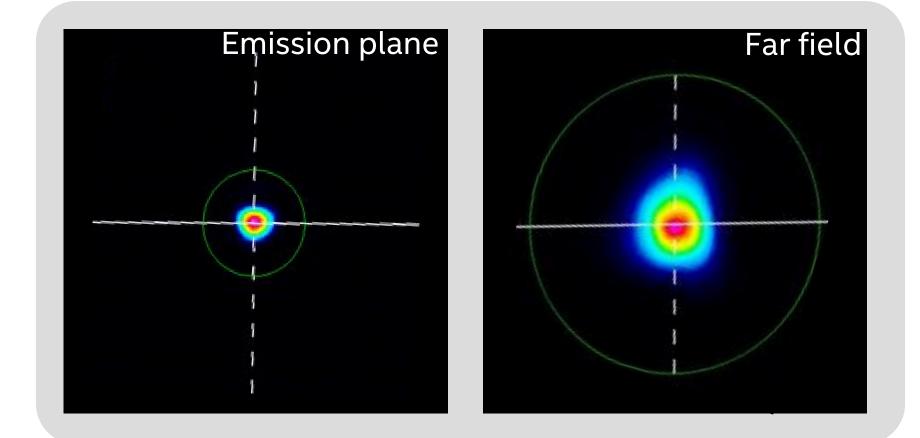

## Optical output to free space

Optical output from chip with M<sup>2</sup> < 1.2

J. Doylend, "Silicon Photonics for LiDAR", SPIE Defense and Commercial Sensing 2021

## FMCW "LiDAR on a chip"

# Integrating 6000+ active and passive components on chip for high volume manufacturing

Mobileye CEO Amnon Shashua shows of the company's new lidar SoC prototype. PHOTOGRAPH: MOBILEYE

https://www.wired.com/story/mobileye-lidar-on-a-chip-intel/

https://www.intc.com/news-events/press-releases/detail/1435/ces-2021-mobileye-innovation-will-bring-avs-to-everyone https://newsroom.intel.com/wp-content/uploads/sites/11/2021/01/Under-the-hood-deck.pdf

Silicon Photonics Product Division

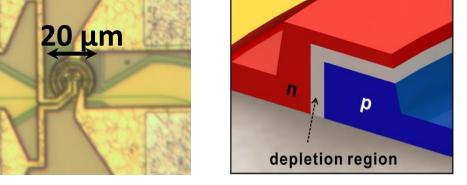

Micro Ring Modulators – A key Component for Sensing

- PN junction design

- High phase efficiency (overlap & optimized doping)→<0.55 V.cm@1310 nm</li>

- Low resistance and capacitance (high RC bandwidth)→50 GHz EO BW

Meer Sakib et al., "260 Gb/s/λ PDM Link with Silicon Photonic Dual-Polarization Transmitter and Polarization Demultiplexer", Tu4D.1, ECOC 2021

EPIC WPTS, San Francisco, January 24<sup>th</sup>, 2022

DC bias vs WL shift

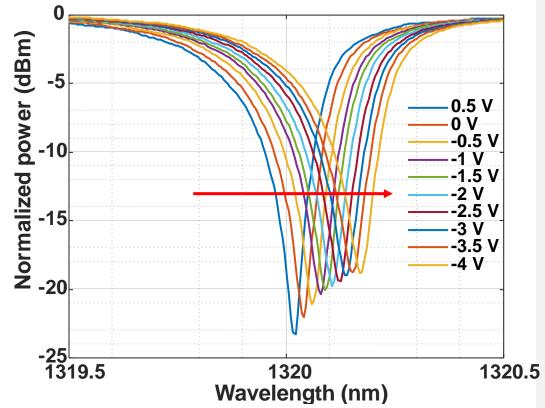

## Micro-Ring Trimming at Wafer Level

- Automated trimming of resonance wavelength at wafer-scale

- Trimming within ±32pm through Ge implantation on to Si waveguide

- Applicable to other components as well

H. Jayatilleka et al., "Post-Fabrication Trimming of Silicon Photonic Ring Resonators at Wafer-Scale", J. Lightwave Tech., 39(5), 5083, 2021

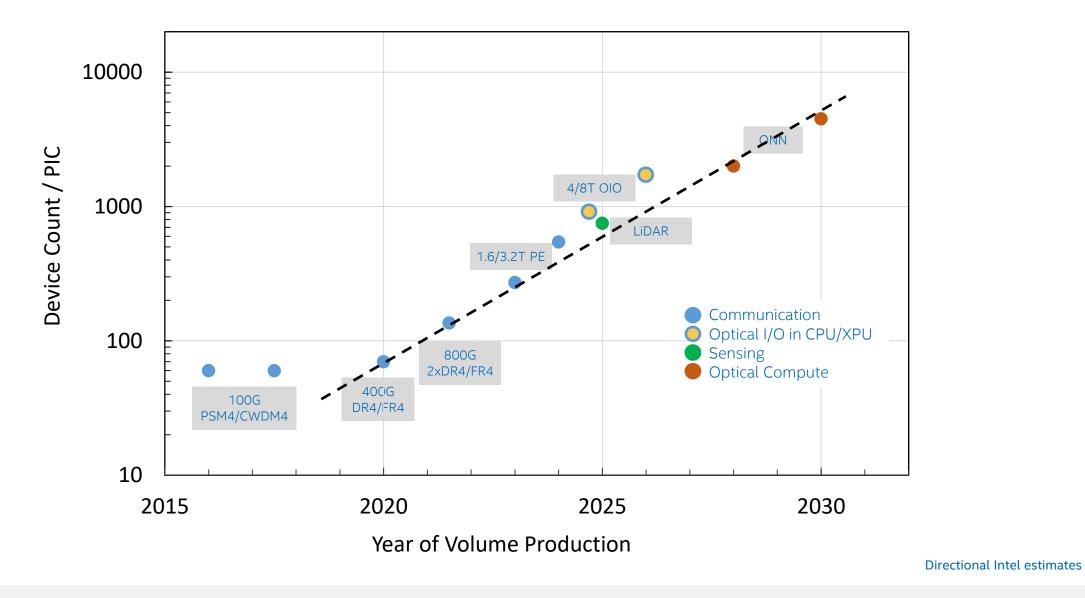

### Silicon Photonics "Moore's Law" Scaling

### Silicon Photonics: An Ideal Platform for Optical I/O and Many Other High-Volume Applications

# Thank You!

### www.intel.com/siliconphotonics

### robert.blum@intel.com

#### **Notices & Disclaimers**

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit www.intel.com/benchmarks. Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure. Your costs and

results may vary.

Intel technologies may require enabled hardware, software or service activation.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.