EPIC Technology Meeting on Electronics & Photonics – Two Sides of One Coin, Munich, Germany, Nov. 14<sup>th</sup> – 15<sup>th</sup> 2022

# W2W and D2W Bonding Technologies Enabling Next Gen Integrated Photonics

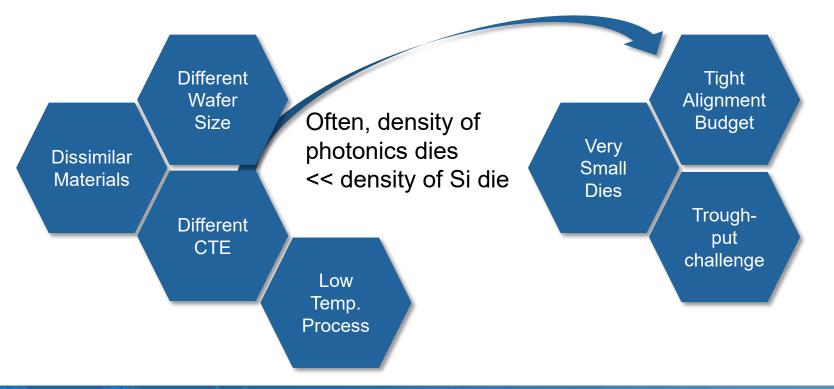

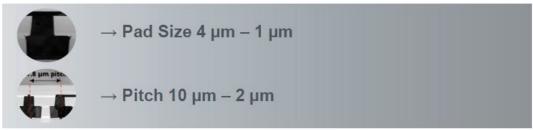

## **Bonding Challenges Related to Photonics**

# Wafer Level

# Die Level (sometimes)

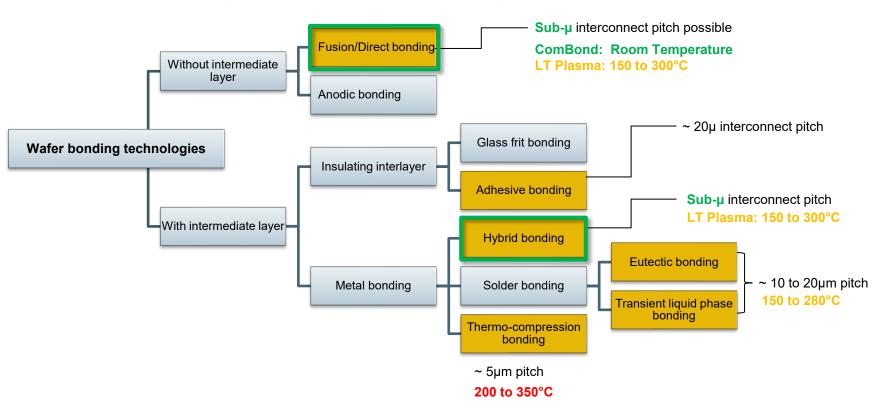

#### **Wafer Bonding Process Options**

#### **Recommended bonding processes for Photonics Integration**

## W2W and D2W Bonding | General Overview

|                      | Collective - D2W  EVG® GEMINI®                                  | Direct Placement - D2W  EVG® 320D2W                                          | Wafer to Wafer  EVG® GEMINI® FB- SmartView® NT3 |

|----------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------|

| Transfer             | Collective Die Transfer by                                      | Direct placement of plasma activated and cleaned dies using Flip Chip Bonder | High Precision Wafer to Wafer Hybrid            |

| Method               | Reconstituted Carrier                                           |                                                                              | Bonding                                         |

| Alignment capability | 1,5 µm proven                                                   | < 1 µm                                                                       | 100 nm                                          |

|                      | 500 nm under development                                        | 200 nm under development                                                     | 50 nm under development                         |

| Challenges           | Cost & Alignment Accuracy                                       | Alignment accuracy<br>Surface cleanliness / Surface<br>preparation           | Integration limitation                          |

| Benefits             | Qualified wafer level equipment for                             | Costs                                                                        | H∀M Qualified process                           |

|                      | plasma activation and cleaning                                  | Integration flexibility                                                      | UPH                                             |

| Maturity             | Application specific volume production proven for several years | Feasibility testing ongoing                                                  | High ∀olume manufacturing                       |

Supporting every integration flow through volume proven surface activation and cleaning process

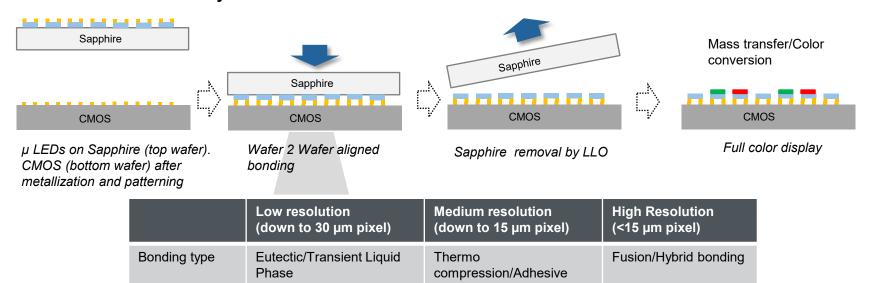

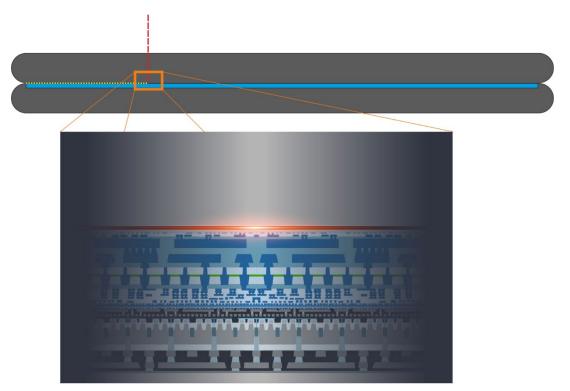

### Wafer to Wafer bonding: Hybridization

#### Role of EVG: Integration of GaN µ LEDs on Sapphire to Silicon CMOS by wafer to wafer bonding

#### Integration

- GaN is grown and patterned on sapphire

- No active CMOS backplane on sapphire

- LEDs need to be integrated with CMOS

#### **Standard Process flow for Hybridization**

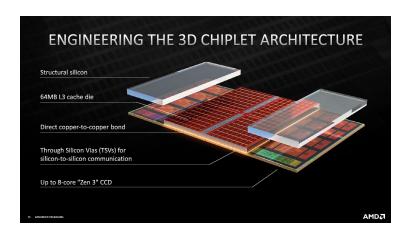

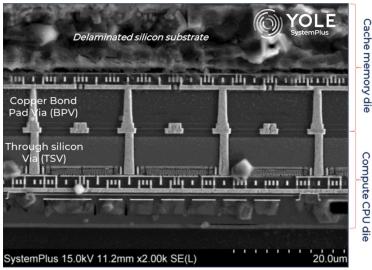

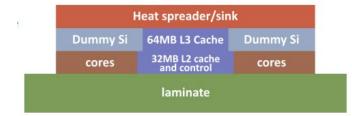

### Hybrid Bonding Example: AMD's V-Cache™

- Using TSMC's SoIC with hybrid Cu-to-Cu bonding in production for desktop and laptop CPUs, gaming

- 3X interconnect energy efficiency (vs. µbump 3D)

- >15X interconnect density (vs. µbump 3D) •

- Thermal is a problem with 3D stacking

- Material selection important

- Which thermal interface material to use and how to select is critical

Package Cross-section #2 - SEM View

## Collective Die-to-Wafer (Co-D2W) Bonding | Process Flow

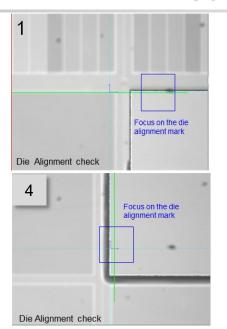

#### Wafer-to-Wafer Bonding **Carrier Separation Carrier Population** Carrier Wafer with D2W Bonding Reconstituted Wafer Glass or Silicon Plasma Activation Plasma Activation Slide-Off or Laser Carrier Wafer (non Adhesive Layer **Target Wafer** Debonding Handler patterned or with alignment marks) Cleaning Handler Cleaning Target Wafer Surface Cleaning Alignment Strategy a. Local alignment key for every die Carrier Flip SmartView Alignment b, Global alignment key for wafer to wafer alignment

| Transfer Method                                           | Pro's                                                                                                                                                                        | Con's                                                                                                                                                                            | Maturity Level                                        |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Collective Die<br>Transfer by<br>Reconstituted<br>Carrier | <ul> <li>Proven technology</li> <li>Die activation and cleaning<br/>equivalent to W2W hybrid bonding</li> <li>Oxide management</li> <li>Reuse of carrier feasible</li> </ul> | <ul> <li>Error propagation of<br/>D2W + W2W alignment</li> <li>Cost of carrier prep,<br/>utilization and clean</li> <li>Die thickness needs to<br/>be in narrow range</li> </ul> | High<br>Volume production<br>proven for several years |

**Hybrid Bonding**

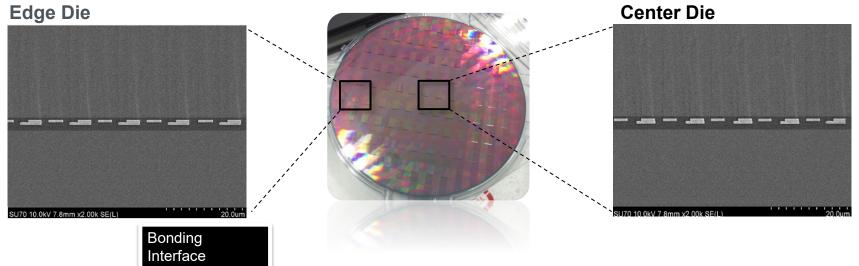

## Co-D2W Bonding | Process Results - Hybrid Bonding

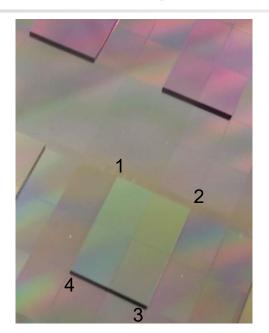

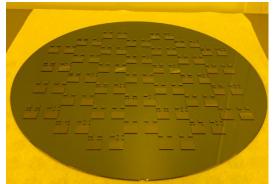

Demonstrator A - 300mm Hybrid Bonding, 5 mm x 7 mm

Demonstrator B - 300mm Hybrid Bonding,10 mm x 14 mm

<sup>\*</sup>Substrates provided under IRT Nanoelec program

## Co-D2W Bonding | Process Results - Hybrid Bonding

| Demonstrator | Die<br>Dimension | Placement<br>accuracy x 3σ | Placement<br>accuracy Y 3σ |

|--------------|------------------|----------------------------|----------------------------|

| Α            | 5mm x 7mm        | 4 O 11m                    | < 2 µm                     |

| В            | 10mm x 14mm      | < 2 µm                     |                            |

## Co-D2W Bonding | Process Results – Hybrid Bonding

- SU70 15.0kV 7.9mm x20.0k PDBSE(CP) 2.00um SU70 15.0kV 7.9mm x100k PDBSE(CP) 500nm

- $\rightarrow$  High Die transfer rate and alignment accuracy < 2 $\mu$ m

- → TEM evaluation of mechanical contact of the bonding pads and Cu grain growth across the bonding interface

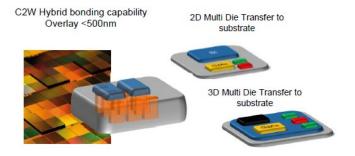

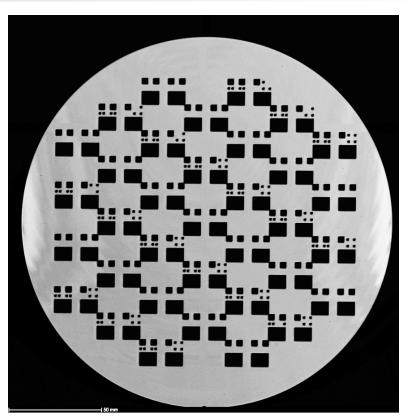

## Co-D2W Bonding | Process Results – Multi Die - Direct Bonding

#### 2D and 3D Multi Die transfer

#### **Demonstrator A**

**Target wafer:** 200mm Thermal Oxide wafer

Collective carrier wafer: 200mm Bare Silicon wafer

#### Die sizes:

- 1x1mm x350µm dies

- 3x3mm x350µm dies

- 7x9mm x350µm dies

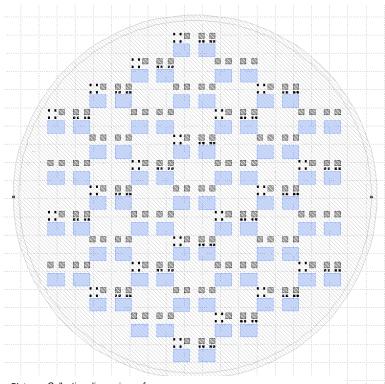

Picture - Collective die carrier wafer map.

## Co-D2W Bonding | Process Results - Multi Die - Direct Bonding

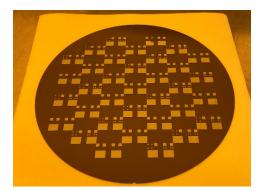

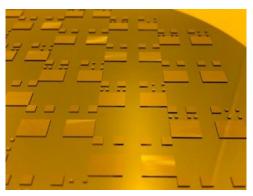

#### Post collective carrier preparation inspection

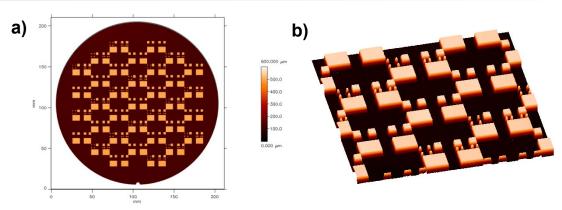

- A high-resolution die height variation (DHV) measurement was performed on the collective carrier with dies after placement using a chromatography sensor to evaluate the die uniformity / distribution.

- A die height variation < 3µm could be observed after collective die carrier preparation.

Picture - Collective die carrier wafers after die placement process.

Die Height variation Measurement - a): Full scan - 2D collective carrier map; b): Detail scan - 3D collective carrier map.

Die Height variation Measurement - a): Detail scan - 2D collective carrier map; b): Detail scan - DHV across the blue line.

Confidential

## Co-D2W Bonding | Process Results - Multi Die - Direct Bonding

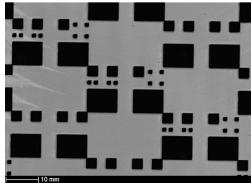

Picture - Target wafer with dies after die transfer process.

High transfer yield including high bonding quality based on Scanning Acoustic microscope images (C-SAM) could be achieved.

**Picture** – Target wafer with dies after die-to-wafer bonding process – die detail..

C-SAM inspection - Post annealing inspection - detail scan.

C-SAM inspection - Post annealing inspection - full scan.

Confidential

# NanoCleave<sup>™</sup> IR Laser Release

## NanoCleave: A New Layer Release Technology

#### **Enables:**

- Use of Si carrier wafers

- Inorganic release layers

- Nanometer precisely defined cleaving planes

- High processing temperatures of stacks

- Room temperature release

- Extremly thin layers

- Applications ranging from advanced packaging to 3D integration to future scaling FEOL integration

#### **EVG NanoCleave**™

#### Technology is demo ready at EVG Headquarter Austria now

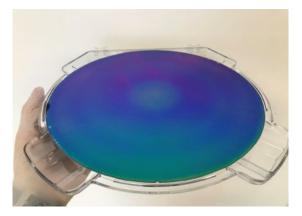

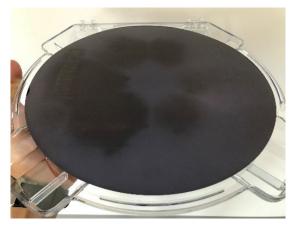

300 mm fusion bonded wafers released

- Layer Transfer of sub-μ layers feasible

- NanoCleave™ release layer may be below EPI growth layer

300 mm molded wafer released

200 mm temporary bonded thin device wafer released

## **Summary**

- Photonic Applications present unique challenges for bonding applications

- D2W and W2W bonding applications co-exist for integration of photonics

- Both D2W and W2W bonding integration schemes benefit from the same bonding mechanisms.

Fusion & hybrid bonding are the most popular bonding interface strategies

- Thin layer handling and release technologies complement bonding applications.

- NanoCleave<sup>TM</sup> is a high temperature stable release technology compatible with Si carrier wafers

#### Disclaimer

The information contained in this document is provided "as is" and without warranty of any kind, express or implied. Any express or implied warranties including, but not limited to, any implied warranty of merchantability, fitness for a particular purpose, and patent infringement or other violation of any intellectual property rights are hereby expressly disclaimed.

EVG makes no representation that the use or implementation of the information contained in this document will not infringe or violate any copyright, patent, trademark, trade secret or other right.

In no event shall EVG be liable for any claim, damages or other liability, including any general, special, indirect, incidental, or consequential damages, whether in an action of contract, tort infringement, misappropriation or otherwise, arising from, out of or relating to the use or inability to use the information.

Acceptance and/or any use of the information contained in this document shall be deemed consent to, and acceptance of, this disclaimer.

#### Confidentiality

Any and all information disclosed during this presentation by EVG is confidential.

Data, design and specifications may not simultaneously apply; or may depend on individual equipment configuration, process conditions and materials and vary accordingly. EVG reserves the right to change data, design and specifications without prior notice.

All logos, company names and acronyms or any combinations thereof, including, but not limited to, EV Group®, EVG® and the Triple i logo, equipment and technology names and acronyms such as GEMINI®, HERCULES®, BONDSCALE®, SmartView®, SmartNIL® and many others, as well as website addresses, are registered trademarks and/or the property of EV Group. For a complete list of EVG trademarks visit www.EVGroup.com/Imprint.

Other product and company names may be trademarks of their respective owners.

Confidential